单片机组件

MCU关键组件介绍

总结单片机中的常见重要组件

1. 看门狗计时器

watchdog timer: https://zhuanlan.zhihu.com/p/149328734

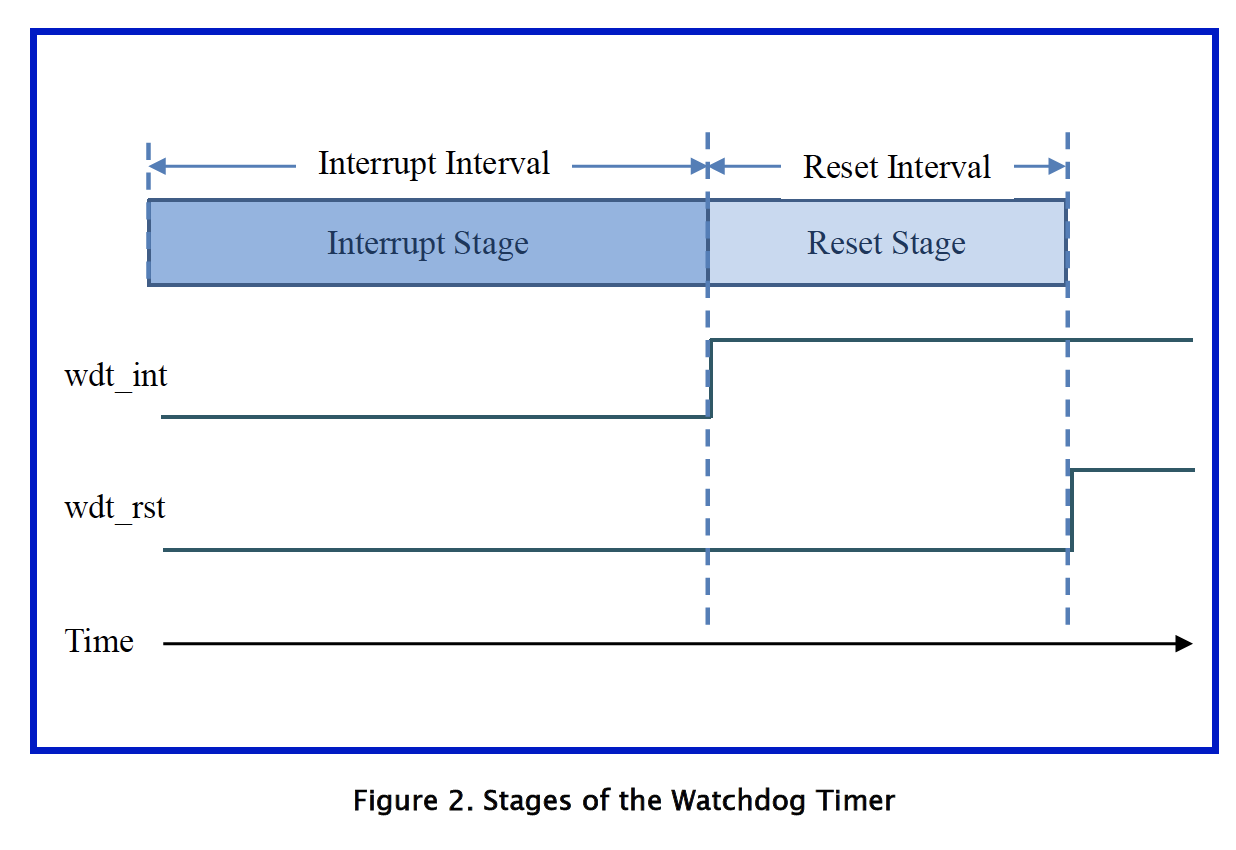

用于在MCU主程序由于硬件或者软件问题时跑飞时强制执行硬件复位或者软件复位,达到故障恢复的目的。没有此项功能时,MCU可能卡死。WDT内部内置一个counter,在counter match产生中断时,cpu应及时清除该counter以及中断,在故障时,cpu无法及时清除counter,导致WDT发起reset,主程序复位。

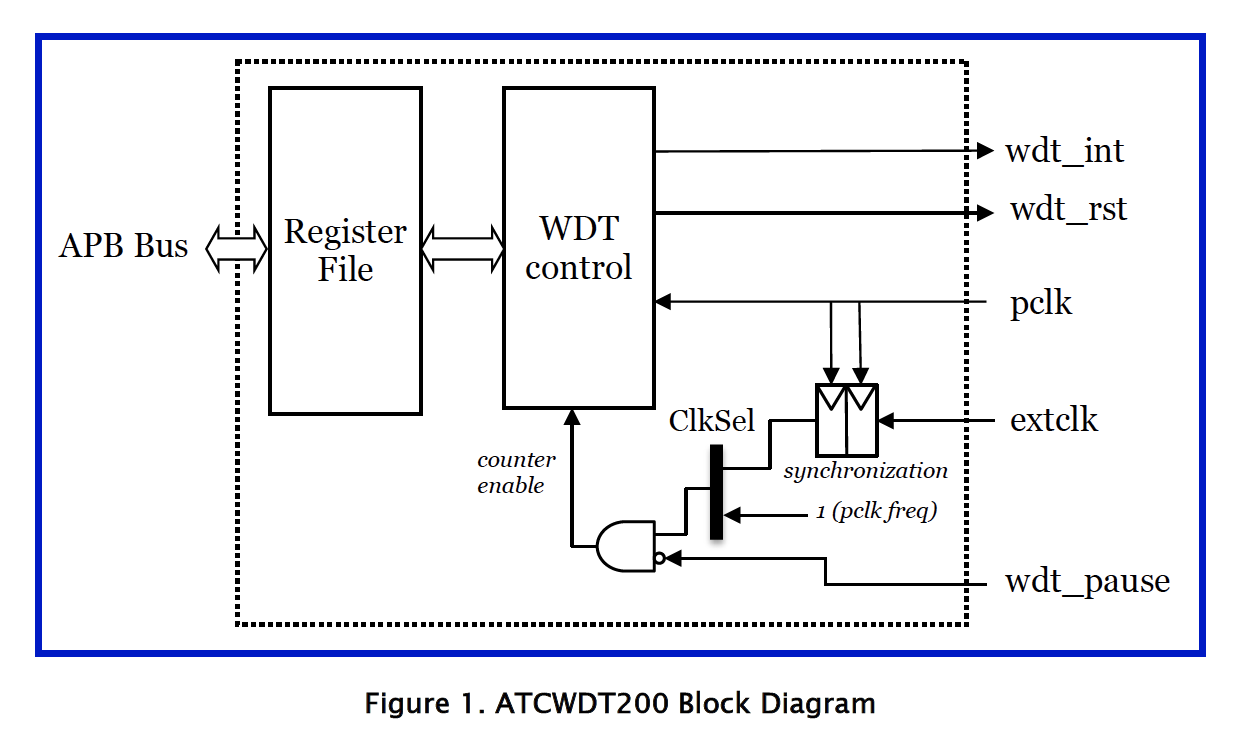

extclk作为data输入,而不是作为时钟,决定了counter enable的频率。WDT可以从pclk或者extclk中选择。中断时间和reset时间均可以由WDT controller寄存器配置。

watchdog需要cpu的参与,因此cpu在watchdog中断信号时必须处于唤醒状态(或者被watchdog中断信号唤醒)

1. interrupt

WDT中断连接至cpu的non-maskable interrupt (NMI),不可被软件disable。这样的配置最大程度上能保证WDT中断的正常执行。

From AndesCore N25f datasheet

Non-maskable interrupts (NMIs) are intended for handling hardware error conditions and are assumed to be non-resumable. They are triggered through the nmi input signal. The rising edge of the signal causes an immediate jump to an address stored in the mnvec register and transition of the privilege level to M-mode, regardless of the state of a hart’s interrupt enable bit.

2. DMA

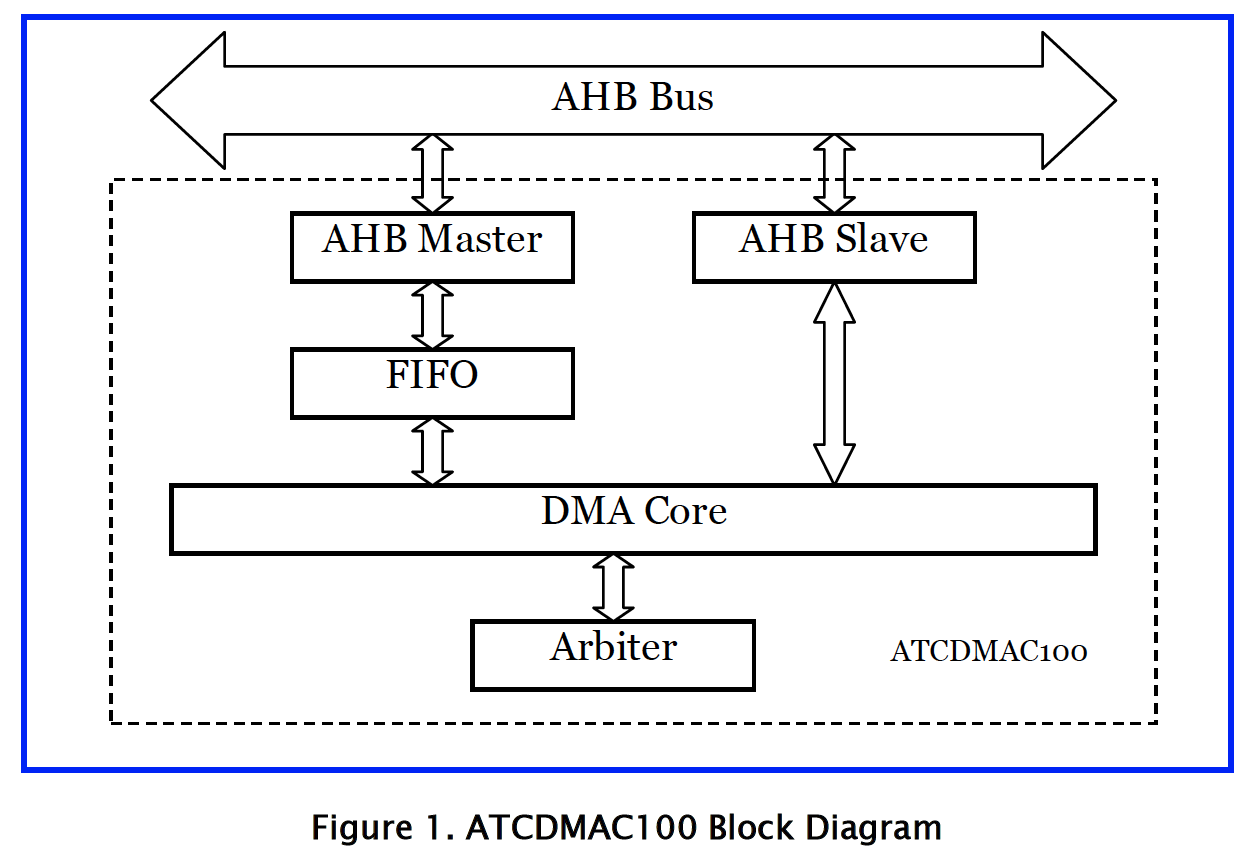

Direct memory access,直接内存访问模块,可以直接通过总线传输数据。将CPU从繁重的数据转移工作中转移出来,从而CPU可以进行更多的计算工作。

常见的AHB master有CPU以及DMA,AHB master可以通过AHB bus对总线上的外设内存直接读取以及写入,因此作为AHB master的DMA也可以搬运数据,减轻了CPU的工作负担。

AHB master:DMA controller主动发起内存数据的传输。

AHB slave:DMA controller同时也是ahb slave,可以被CPU读写寄存器控制DMA。

1. 工作流程

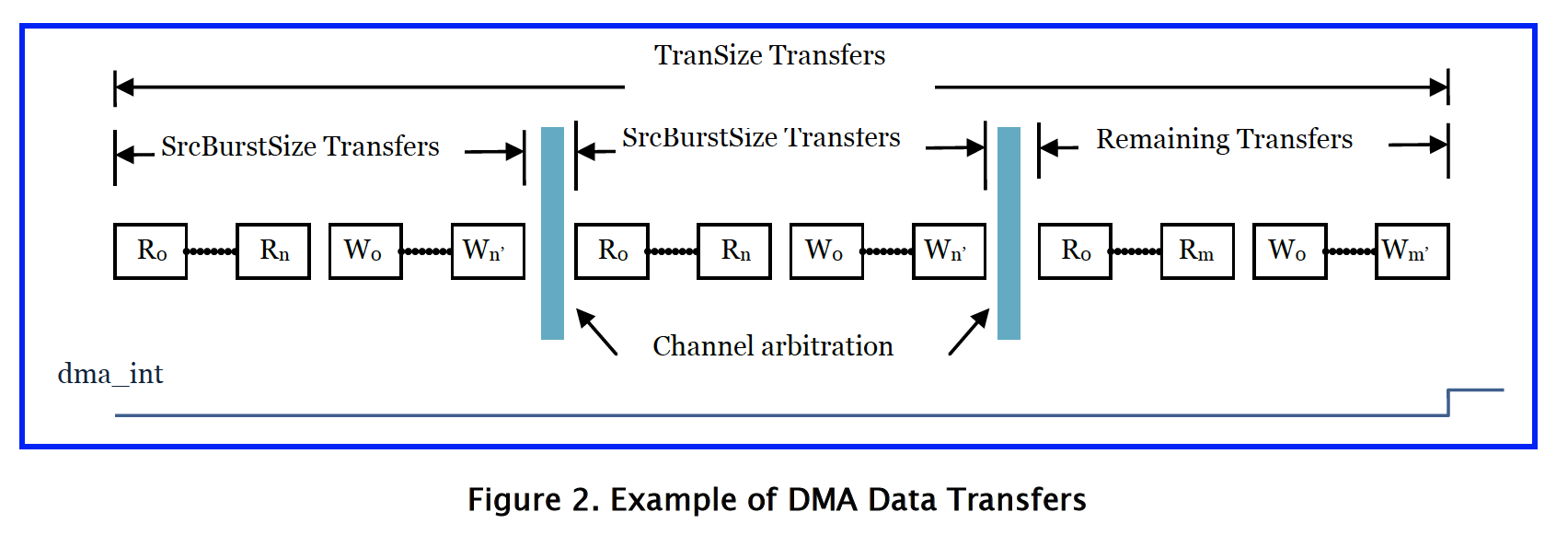

Andes DMA controller提供8个DMA channel,每个channel均可独立配置,DMA controller通过仲裁器,优先为高优先级(channel优先级可配置,同优先级的轮询调度)的channel执行单个transaction,DMA transfers可由多个transactions构成。

在DMA transfers执行完成或出现错误或放弃时,产生DMA中断交由CPU处理。

DMA传输支持三种地址控制模式,递增递减以及固定地址。固定地址可以与如uart进行数据传输,固定地址绑定到uart的THR或者RBR寄存器。

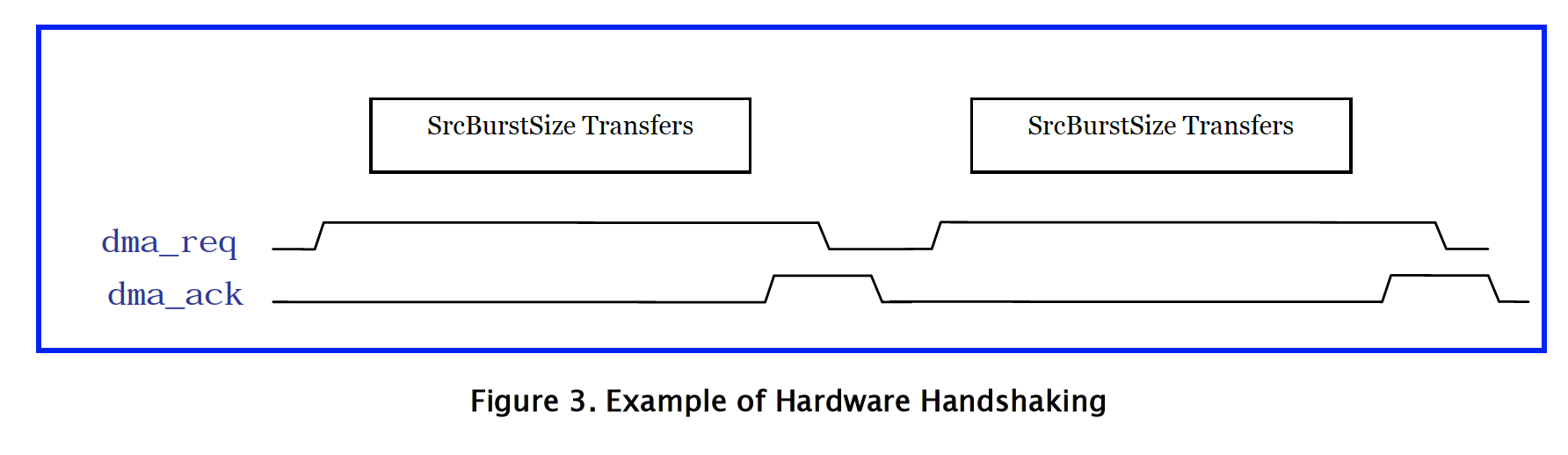

2. Hardware Handshaking

提供给低速设备的一套最多32组的硬件握手信号dma_req/dma_ack,由dma_req控制数据的传输,数据传输完成后拉高dma_ack。避免由于低速设备导致AHB bus被长时间占用。如从uart RX FIFO搬运数据时,如RX FIFO数据量达到一定阈值时会触发dma_req信号。

每个channel的控制寄存器均可配置该channel选择的握手信号pair,channel数据传输由该pair控制。并可配置是否启动握手模式。

1 | |

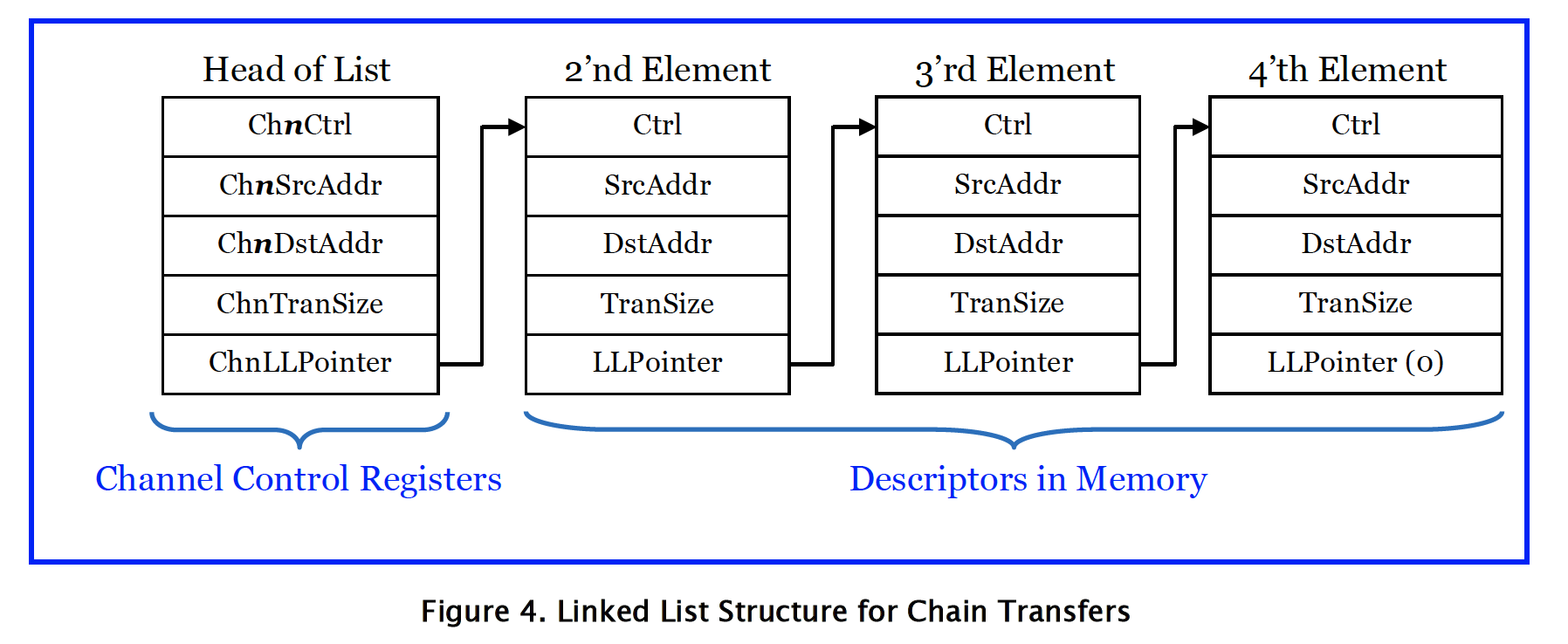

3. DMA链式传输

DMA一般只提供原地址,目标地址,数据长度以及transfer size,这样单个DMA transfers只能搬运连续内存地址的数据。ATCDMAC100提供了链式传输的配置,通过一个链表,其中包含了下一块需要搬运内存的地址

interrupt handling software需要在中断产生后重新使能该channel即可继续链式传输。

本博客所有文章除特别声明外,均采用 CC BY-SA 4.0 协议 ,转载请注明出处!