serial

串口基础

同步通信是指,发送方发出数据后,等接收方发回响应以后才发下一个数据包的通讯方式。

异步通信是指,发送方发出数据后,不等接收方发回响应,接着发送下个数据包的通讯方式。

换句话说,同步通信是阻塞方式,异步通信是非阻塞方式。在常见通信总线协议中,I2C,SPI属于同步通信而UART属于异步通信。同步通信的通信双方必须先建立同步,即双方的时钟要调整到同一个频率,收发双方不停地发送和接收连续的同步比特流。异步通信在发送字符时,发送端可以在任意时刻开始发送字符,所以,在UART通信中,数据起始位和停止位是必不可少的。

UART

Universal Asynchronous Receiver/Transmitter (UART)

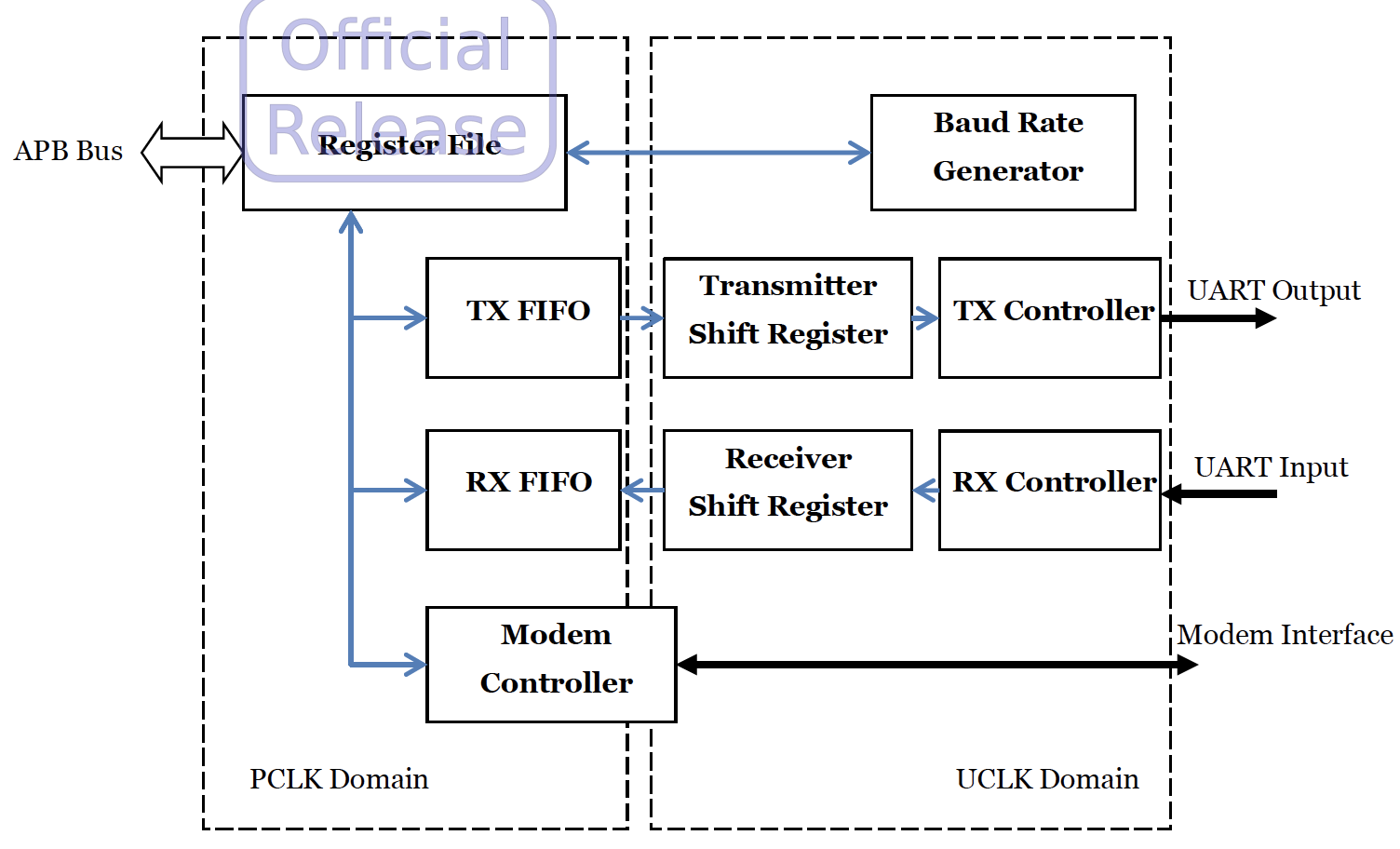

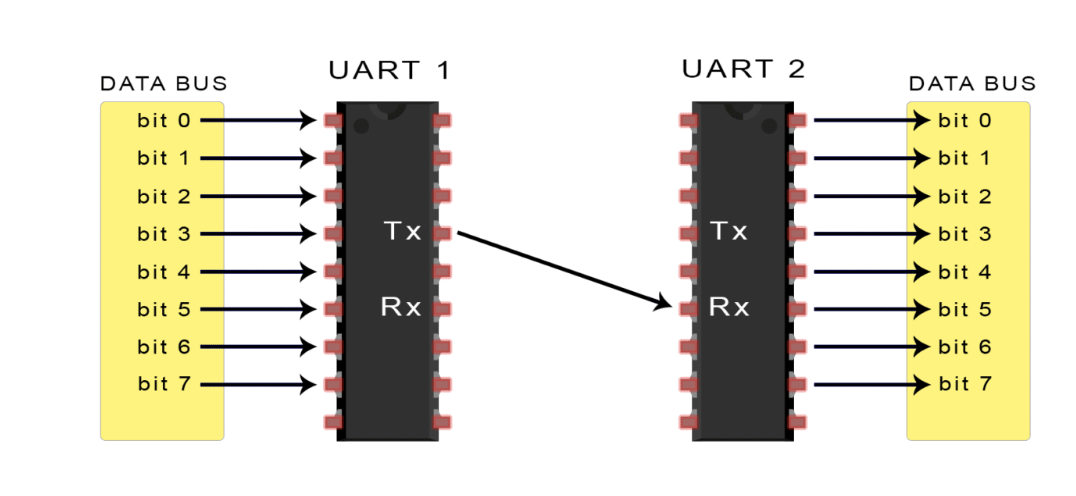

UART是对称异步通信串口。发送端在任意时刻均可发送数据,接收端若未及时接收则数据丢失。可以看出异步通信要求双方提前等待数据的传输(串口的速度远低于CPU的速度),从而避免数据丢失。UART通信只需要两条导线。

UART通信的基本要求是:

- UART双方保持一致的波特率以及数据包配置,不需要保持一致的时钟频率

- UART双方TX连接到对方的RX

1. Transmitter

包含一个Transmitter FIFO (TX FIFO),Transmitter Shift Register (TSR),和Transmitter Controller (TX controller)。用于向外界的UART口传输比特流,FIFO以及buffer只用作输出时的缓存,接收端只是被动接受。接收端未及时接收则数据丢失。

1. Transmitter FIFO (TX FIFO)

存储着需要传输的数据,APB BUS通过写入THR寄存器,可以向FIFO中添加数据。可以软件外置一个buffer,从buffer中向FIFO同步,达到软件上提升FIFO容量的目的。

2. Transmitter Shift Register (TSR)

TSR移位寄存器每次从FIFO中获取一个字,并将并行数据转换为0101的串行的比特流。

3. Transmitter Controller (TX controller)

TX controller为比特流添加开始结尾以及奇偶校验信息后输出该比特流至IO pad上。IO pad可以外接到外部的UART RXD引脚。外部的UART 通过该RXD引脚接收芯片UART口的TXD引脚比特流,并解析得到数据。

2. Reciever

包含Receiver FIFO (RX FIFO), Receiver Shift Register (RSR), 和Receiver Controller (RX Controller)。接收端接收外界UART TXD口输入的比特流

1. Receiver Controller (RX Controller)

RX Controller通过过采样时钟采样输入的比特流(每个过采样率下采样一次)并校验,这个过程与TX controller相反。要求两个UART有相同的波特率。

2. Receiver Shift Register (RSR)

RX Controller获取的比特流通过RSR移位寄存器转换为字存储至RX FIFO中。

3. Receiver FIFO (RX FIFO)

CPU可以通过读取RBR寄存器来读取FIFO中的数据。同样可以软件外置一个buffer来提升RX FIFO的容量。与TX FIFO不同的是,RX FIFO能够缓存数据,FIFO以及buffer满后,后续的数据会丢失。Receiver FIFO接收到一定的数据后会触发中断,CPU执行中断程序搬运FIFO数据至buffer。

3. 波特率

uart的波特率即传输bit的速度,通过uart clock分频生成Baud Rate Generator clock,由此clock在oversampling ratio下,每oversampling ratio个cycles对同一个输入bit采样,以及生成对应波特率的输出bit流。

reciever和transmitter的波特率必需配置相同才能正确的通信。

过采样

即对单个数据采样多次,Baud Rate Generator clock在每个cycle下采样,对同一个bit采样oversampling ratio次。START BIT只有半个周期,即只会被采样oversampling ratio / 2次。

一定的过采样能够有效的抑制时钟周期不稳定对数据传输的影响。

4. Modem controller

不被大多数的UART设备使用

提供自动的数据流控制功能,通过一组RTS(Request to send)/CTS(Clear to send)信号连接到对应UART的该信号上(RTS连接到CTS,CTS连接到RTS)。通过控制RTS的信号值,控制通信对方UART CTS值,CTS拉低时不再继续传输数据,达到控制数据流的作用。

TXFIFO里有数据的时候,如果没有flow control,数据则会立即被发送出去。

5. DMA

可以为RXFIFO或者TXFIFO在某个阈值下触发DMA操作。对于transmitter,可以配置DMA将芯片某处数据搬运至THR寄存器,从而向外传输数据。对于reciever,DMA 将RBR寄存器数据搬运值芯片某处,达到读取uart的效果。

DMA搬运数据不依赖总线以及CPU,能够节省CPU时间。

6. 中断

uart有多个中断信号,可以将所有中断信号or后输出至CPU,使得一个uart设备只占用一个中断。在中断处理程序IRQ中对多个uart中断信号分开处理。

- Receiver line status:传输过程中的错误导致的中断或数据overrun丢失,读取LSR寄存器后清空

- Received data available:RXFIFO数据量超出阈值,读取RBR寄存器至低于阈值后清空

- Character timeout: RXFIFO初始态,读取RBR寄存器后清空

- Transmitter Holding Register empty:transmitter FIFO置空。重新写入字清空。

- Modem status:调制解调器事件发生,如CTS被拉低

uart中断可以很好的触发内置FIFO和软件外置bufferd的数据同步,如在Received data available时读取RXFIFO数据至外置buffer,或者在Transmitter Holding Register empty时从外置的buffer中取数据写入TXFIFO。

GPIO

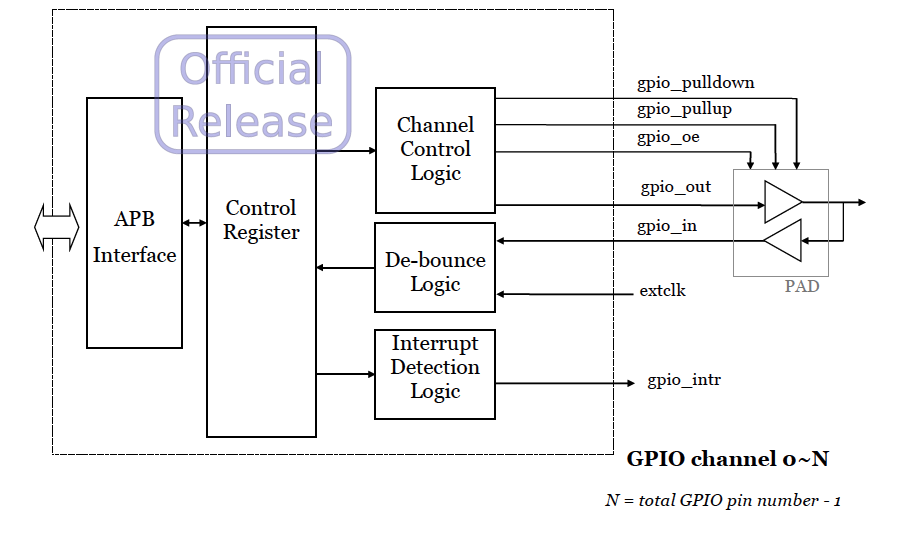

General purpose I/O (GPIO) 通用输入输出

GPIO作为通用的输入输出口,可以由软件配置为输入或者输出,或者即是输入也是输出。通俗地说,就是一些引脚,可以通过它们输出高低电平或者通过它们读入引脚的状态是高电平或是低电平。一定程度上能够复用芯片上不多的pin,达到输入和输出的目的。

每个GPIO channel可以单独配置为输入或输出,作为输入时GPIO controller对输入信号采样,降噪(de-bounce),产生中断。作为输出时可以在pull-up或者pull-down配置下输出信号。

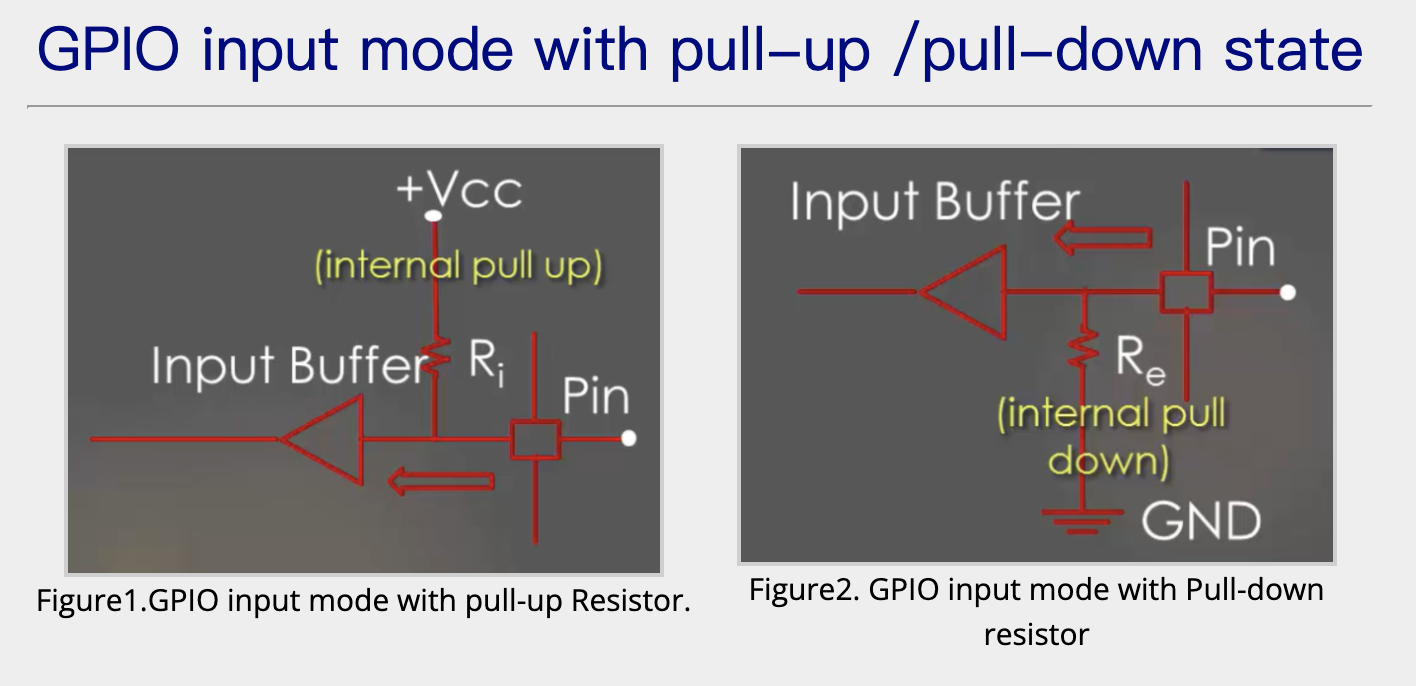

1. pull-up和pull-down

理解什么是上拉电阻和下拉电阻

避免由于输入pin处于floating状态下不确定的电平,使用上拉电阻将输入默认至高,下拉电阻将输入默认至低。在某个pin浮动时通过一个电阻将其状态确定下来。

IO端口通常会有一些配置上拉下拉的选项。

2. GPIO signals

gpio_in[N:0] Input PAD GPIO input data

gpio_oe[N:0] Output PAD GPIO output data enable signal. Active high(channel direction register作为输出)

gpio_out[N:0] Output PAD GPIO output data

gpio_pullup[N:0] Output. PAD GPIO output pull-up enable signal

gpio_pulldown[N:0] Output PAD GPIO output pull-down enable signal

gpio_intr Output Interrupt controller ATCGPIO100 interrupt signal

extclk Input Clock generator External de-bouncing clock source. The clock source must be at least 4x slower than pclk.

3. channel control

寄存器控制每个GPIO channel,包括输入输出数据,以及pull类型配置。

4. de-bounce control

寄存器控制输入降噪,包括每个channel降噪开启,降噪时钟源的选择,以及降噪的scale

5. interrupt control

寄存器控制中断,包括中断的开启,中断状态,以及每个channel的中断触发模式(高电平,低电平,上升沿,下降沿,dual edge)。通过中断来调用CPU处理GPIO的输入数据。

6. usage

GPIO通常作为通用的IO输入输出,通常最终会被连接到芯片的输入输出引脚上。由于不只是GPIO需要输出,像uart, spi以及芯片内部的信号需要输出,经常输出引脚的数量低于需求量。因此可以在芯片内设置IOmux,通过寄存器选择需要输出的信号,达到IO pad有效复用的目的。

可以说IO pad里实现了一个GPIO,通过与内部的ATCGPIO控制的GPIO通信,同时也可以在硬件中配置与其他的信号相互连接。

本博客所有文章除特别声明外,均采用 CC BY-SA 4.0 协议 ,转载请注明出处!